DAIレシーバを作ろう

(ついでに動作確認用DACも作ろう)

ディジタル音声はS/PDIFインタフェースで送受信する

ってのは多分ご存知かと思います。

実はこのS/PDIF、

・ディジタルデータ本体

・ディジタルデータ列のビット区切り位置を示すクロック

・今送っているデータが左か右かという識別信号

(1ワードあたりのビット数やサンプリング周波数の伝達も兼ねる)

・複製禁止とかの各フラグ類

を1組の信号線で送れるよう合成したものなんですな。

D/AコンバータICに注入するデータやクロックはそれぞれが分離してないといけないので、S/PDIFを受信してデータと各種クロックを分離する回路が

必要です。

この回路をDAIレシーバというのですが、これがないとDACが動作しないので、新規にこしらえます。

シーラスロジックのCS8416なら比較的簡単に入手できるので、これを使いました。

デー

タシートを参考にして、回路はこのようにしました(しかし読みづらいデータシートだよねこれ)。

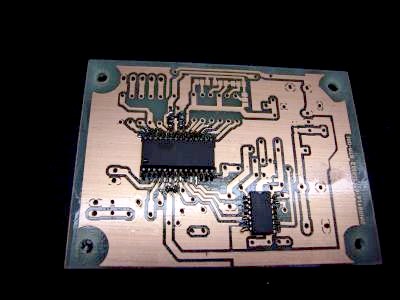

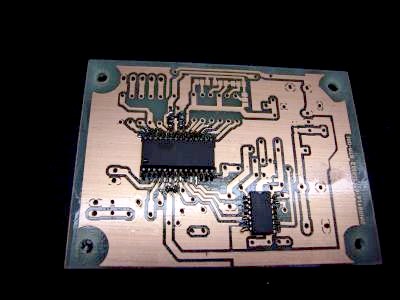

10cm×7.5cmの片面基板でつくることができます。

回路図(png)

部品

配置図(部品面より、

png) 上面の赤い線は、ジャンパ線で接続する箇所です。

感光基

板フィルム(部品面より透

視、720dpi、png)

基板があまったので、TDA1543を使った動作チェック用DACも

作りこんであります。

フィルムはよく乾燥させた後でインク面と銅箔面が密着するように重ねて感光させてください。

5V単電源で動作します。

部品表

| 番号 |

品

名 |

記事 |

入手先 |

| IC1 |

TA48033S |

3.3Vシリーズレギュレータ |

|

| IC2 |

CS8416CSZ |

ディジタルオーディオレシーバ |

千石・共立・Digi-Key |

| IC3 |

S-80827CNY |

リセットIC(2.7V) |

マルツ |

| IC4 |

74HC14D |

1.27mm表面実装シュミットインバータ(TC74HC14AF等) |

|

| R1 |

3KΩ |

金属皮膜 1/8〜1/4W |

|

| R2 |

75Ω |

1/8〜1/4W |

|

| R3 |

22KΩ |

1/8〜1/4W |

|

| R4〜R15 |

47KΩ |

1/8〜1/4W |

|

| R16 |

510Ω |

1/8〜1/4W |

|

| R20 |

47KΩ |

1/8〜1/4W |

|

| D1 |

10DDA10等 |

汎用整流ダイオード 1A |

|

| C1 |

1000pF(102) |

フィルム |

|

| C2 |

0.022uF(223) |

フィルム |

|

| C3 |

1uF |

0.1uF〜1uF 積層セラミック(1608サイズ) |

秋月 |

| C4 |

33uF |

一般アルミ電解 6.3V以上 |

|

| C5 |

0.01uF(103) |

0.01uF〜0.047uF フィルム |

|

| C6 |

0.01uF(103) |

0.01uF〜0.047uF フィルム |

|

| C7〜C9 |

1uF |

0.1uF〜1uF 積層セラミック(1608サイズ) |

秋月 |

| C10 |

1000uF |

一般アルミ電解 10V以上 |

|

| C11 |

220uF |

一般アルミ電解 6.3V以上 |

|

| C12 |

33uF |

一般アルミ電解 6.3V以上 |

|

| C13 |

0.01uF(103) |

0.01uF〜0.047uF フィルム |

|

| C14 |

4.7uF |

一般アルミ電解 10V以上 |

|

| C15 |

1uF |

0.1uF〜1uF 積層セラミック(1608サイズ) |

秋月 |

| L1〜L2 |

フェライトビーズ |

BL01RN1A1D2B(ムラタ/マルツ扱い)他 |

|

ジャンパおよびコネクタ

CN1 COAX IN

同軸ディジタル入力を接続する端子で、基板上で75Ω終端がなされています。

使用しない場合はオープンにしてください。

CN2 OPT IN

TOSLINKで受けたロジックレベルのディジタル入力を接続します。

ここの電圧はCS8416のロジックインタフェース電圧(デフォルトで3.3V)を超えてはならないことに注意してください。

使用しない場合はオープンにしてください。

CN3 SERIAL OUT

クロック分離後のシリアルデータ出力です。デフォルトで3.3V CMOSレベルになっていますが、5V

CMOSに改造することもできます。通常はI2Sフォーマットですが、左詰めや右詰めも選べます。

CN4 電源コネクタ

+5Vを供給します。

CN5 INPUT SEL

使用する入力端子を選択します。

ショートするとCOAX IN、オープンでOPT INよりデータを取り込みます。

CN6 MUTE

正常にS/PDIFデータを受信できなかった、または受信したデータにVフラグが立っている場合に「H」レベルになります。

DACデバイスと接続して、異常時にミュートさせるために使うことができます。

CN7 /MUTE

CN6の論理を反転したものです。

CN8,9 PWR+,GND

CS8416のロジックインタフェース電源と同じ電圧が出力されます。

DACデバイスにディジタル電源を供給するために使うことも可能です。

CN10 /RESET

トーテムポール出力のリセット信号で、電源投入後一定時間「L」レベルになります。パワーオンリセットを必要とする他の回路にリセット信号を提供すること

ができます。

JP1 +5V

CN4のホット側に直結しており、CS8416を5Vロジックインタフェースに改造する際に使用します。

本基板を5Vロジックインタフェースに改造するには、L2を除去してCN8とJP1を接続してください。

SJ1,4 SFSEL

デフォルトでI2Sになるよう短絡してありますが、左詰め24bitや右詰め24bitも選択できます。

必要であればショート箇所をカッターで切って反対側をハンダで短絡してください。

SJ2 128/256fs

システムクロック出力(RMCK)の周波数倍率を設定します。

デフォルトは256fsです。48kHz以下のサンプリング周波数では128fsに対応しないディジタルフィルタやDACがあるので、変更の際はそれらの

データシートを確認してください。

一方、FN1242Aなどの場合は128fsに変更しておくとサンプリングレート32〜192kHzのすべてに対応できるようになります。

SJ3 EMPH

CS8416はディジタル式のディエンファシスフィルタを内蔵しており、デフォルトでは有効にしてあります。

CS8416をハードウェアモードで使っている都合上、ソースがエンファシスであるかどうかを外部に通知できません。そのためCS8416内部で行う以外

選択的にディエンファシスをかける手段がなく、特別な事情がなければ有効のままにしておいてください。

あとは別基板にDACデバイスやアナログ回路を載せて、とっかえひっかえする楽しみ方ができるのではないかと思います。

戻る